# ADUC 烧录器

## 使用说明

版 本号: V4.1

#### 版权所有©

### 西安恩狄集成电路有限公司

本资料内容为西安恩狄集成电路有限公司在现有数据资料基础上编制而成,本资料中所记载的实例以正确的试用方法和标准操作为前提,使用方在应用该等实例时应充分考虑外部诸条件,西安恩狄集成电路有限公司不担保或确认该等实例在使用方的适用性、适当性或完整性,西安恩狄集成电路有限公司亦不对使用方使用本资料所有内容而可能或已经带来的风险或后果承担任何法律责任。文档中所有涉及到第三方软件的,请自行购买正版软件,因第三方软件版权问题涉及到的一切后果,与西安恩狄集成电路有限公司无关。基于使本资料的内容更加完善等原因,西安恩狄集成电路有限公司保留未经预告的修改权。

西安恩狄集成电路有限公司

地 址:陕西省西安市高新区高新一路 19 号思安大厦 501

电 话: + (86 29) 88322766 网 站: www.admicrochip.com

微信号: 恩狄 ADUC

## 版本修订记录

| 版本号  | 变更内容                                     | 变更时间      | 变更人 |

|------|------------------------------------------|-----------|-----|

| V1.0 | 初版                                       | 2022/4/2  | 毛金鹏 |

| V3.0 | 添加配置卡的使用方法;添加接线烧录。                       | 2022/5/16 | 毛金鹏 |

| V4.0 | 添加 16F01、18F06、16F02、18f08 配置卡使用;添加接线烧录。 | 2023/2/9  | 辛文强 |

| V4.1 | 添加 16F02 注意事项                            | 2023/4/7  | 辛文强 |

|      |                                          |           |     |

|      |                                          |           |     |

#### 目录

| 版本修订记录                         | 1  |

|--------------------------------|----|

| 1. 烧录器和工具简介                    | 3  |

| 1.1. ADUC 烧录器简介                | 3  |

| 1.2. 配套工具简介                    | 4  |

| 1.3. 工具检查                      | 5  |

| 2. 烧录                          | 7  |

| 2.1. 烧录准备                      | 7  |

| 2.2. 固件更新                      |    |

| 2.3 配置卡烧录                      | 10 |

| 2.3.1 配置卡使用说明                  | 10 |

| 2.3.2 在线烧录                     | 15 |

| 2.3.3 脱机烧录                     | 20 |

| 2.4 接线烧录                       | 22 |

| 2.4.1 1605、1606、1607 接线烧录      | 22 |

| 2.4.2 16H02 接线烧录               | 24 |

| 2.4.3 18F02、18F020、18F022 接线烧录 | 25 |

| 2.4.4 16F01 接线烧录               |    |

| 2.4.5 18F06 接线烧录               |    |

| 2.4.6 18F08 接线烧录               |    |

| 2.4.7.16F02 接线烧录               | 32 |

## 1. 烧录器和工具简介

#### 1.1. ADUC 烧录器简介

新版的 ADUC 烧录器(下图 1)支持西安恩狄集成电路有限公司现有的所有芯片型号,配合 MCU-ISP 上位机软件(下图 2)使用。通过给烧录器更新对应芯片的固件,实现烧录不同系列芯片的功能。通过对配置卡上跳线帽的调整和芯片烧录座位置的改变,实现对同一型号、不同封装的芯片进行烧录的功能。

图 1. 烧录器实物

**图 2.** MCU-ISP 软件主界面 第 3 页 共 33 页

## 1.2. 配套工具简介

1.2.1: 电源: 烧录器需使用类似于如下图的 12V 的电源供电。

图 3

1.2.2: USB 线: 连接电脑和烧录器,用来更新固件和下载烧录文件。

图 4

1.2.3: 配置卡: 目前有三种, 配置卡-01(烧录 16H02)、配置卡-02(烧录 1602、1605、1606、1607)、配置卡-03(烧录 18F02/18F020/18F022)、配置卡-04(烧录 16F01)、配置卡-05(烧录 18F06)、配置卡-06(烧录 18F08)、配置卡-07(烧录 16F08)。

图 5

1.2.4: 彩虹线: 机台烧录时使用。

图 6

## 1.3. 工具检查

- 1.3.1: 确认上述的配套工具是否具备,除彩虹线外(上机台使用)其他必须具备。

- 1.3.2: 向上/向下扳动锁紧座杆,检查锁紧座是否可以正常使用。

图 7

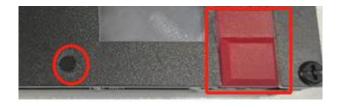

1.3.2: 确认红圈和红框位置的两个按键能否正常按下。

图 8

1.3.3: 在烧录器右侧边位置插上电源,上电后确认显示屏可以正常显示。

图 9

## 2. 烧录

## 2.1. 烧录准备

- 2.1.1: 确认需要的工具都具备; ISP 软件是官网最新版本。

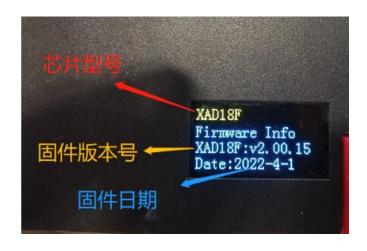

- 2.1.2: 登录<u>西安恩狄官网固件</u>,界面如下图 3,查看对应芯片型号的最新固件;然后烧录器上电,显示屏信息如下图 4,确认烧录器中的固件是否是对应芯片的最新固件,不是最新的固件从官网下载最新的固件按照 2.2 节的内容进行固件更新。

| www.xad-ic.com/html/shaoluqi/index.html |        |            | □ ■ A <sup>N</sup> 5 |

|-----------------------------------------|--------|------------|----------------------|

| AD1607烧录固件(仅适用于绿色版本烧录器)                 | V1.01  | 2022-05-06 | AD1607               |

| AD1607烧录固件(仅适用于黑色ADUC版本烧录器)             | V2.00  | 2022-05-06 | AD1607               |

| AD1605烧录固件(仅适用于黑色ADUC版本烧录器)             | V2.0.0 | 2022-05-05 | AD1605               |

| AD1605烧录固件(仅适用于绿色版本烧录器)                 | V1.01  | 2022-05-05 | AD1605               |

| AD1606烧录固件(仅适用于黑色ADUC版本烧录器)             | V2.00  | 2022-04-16 | AD1606               |

| AD1606烧录固件(仅适用于绿色版本烧录器)                 | V1.021 | 2022-04-15 | AD1606               |

| AD18F02烧录固件(仅适用于黑色ADUC版本烧录器)            | V2.00  | 2022-04-12 | AD18F02              |

| AD18F02烧录固件(仅适用于绿色版本烧录器)                | V1.10  | 2022-03-11 | AD18F02              |

| AD18F022烧录固件(仅适用于绿色版本烧录器)               | V1.09  | 2021-12-16 | AD18F022             |

图 3. 恩狄官网固件

图 4. 显示屏固件信息

#### 2.2. 固件更新

2.2.1: 连接 USB: 在烧录器右侧边位置,电源插口旁边有 USB 接口,使用如图所示的 USB 线,红框位置(较宽的口)连接电脑,蓝框位置(较窄的口)连接烧录器 USB 口。

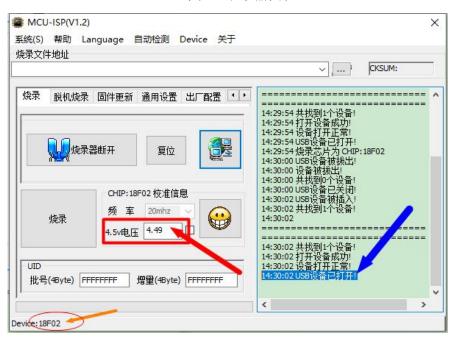

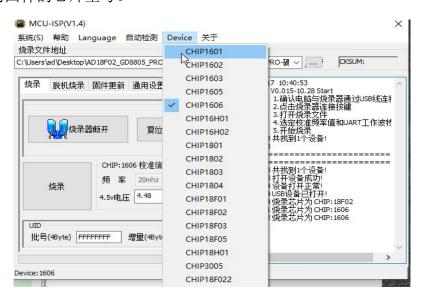

2.2.2: 上位机 ISP: 打开 MCU-ISP 上位机软件 exe (官网下载最新版本),在 Device 中选择想要更新的固件的芯片型号。

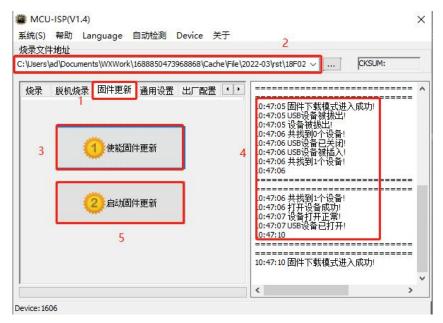

2.2.3: 开始更新: 固件更新界面如下图 6 所示,首先点击图 6 中 1 处的固件更新,查看烧录器显示屏,烧录器显示屏的界面内容显示为下图 5 所示的界面后。点击图 6 中 2 处的文件选择按钮,选择更新芯片型号对应的固件;选择好之后,点击图 6 中 3 处的"使能固件更新"按钮;当 ISP 右侧出现图 6 中 4 处的内容时;点击 5 处的"启动固件更新"按钮,当 ISP 右侧界面出现下图 7 的内容时,证明固件更新成功。

图 5. OLED 固件更新信息

第 8 页 共 33 页

图 6. ISP 固件更新界面信息

图 7. ISP 固件更新成功信息

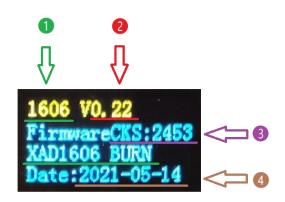

2.2.4: 固件信息解读:不插 USB 重新上电,此时烧录器显示屏上的信息如图所示,观察烧录器 OLED 屏幕上的显示信息,确认使用的固件符合要求。绿色 1 指示的文字表示烧录固件支持的芯片型号;红色 2 指示文字表示烧录器固件版本号;紫色 3 指示文字表示烧录器内部脱机烧录程序的校验码:棕色 4表示烧录器固件生成日期。

图 8. OLED 上电屏幕信息

第 9 页 共 33 页

## 2.3 配置卡烧录

#### 2.3.1 配置卡使用说明

2.3.1.1: 烧录芯片时需要用到配置卡,插配置卡时配置卡红圈位置的三角标对着烧录器左侧红框位置的三角标,配置卡红框位置靠近烧录器的锁紧座,将配置卡排针插入烧录器蓝框位置的排母中。

- 2.3.1.2: 配置卡具体使用方法: 配置卡支持烧录座可以插到锁紧座上的芯片封装,不支持的封装见 2.4 接线烧录。

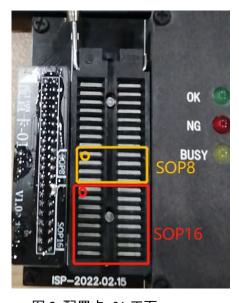

- 2.3.1.2.1、配置卡-01: 烧录 16H02 芯片。支持封装 SOP16、SOP8。

图 10. 配置卡-01 背面

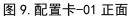

将配置卡-01 插到 ADUC 烧录器上之后,正面图如图 9 所示,背面如图 10 所示.

| 封装     | 背面跳线帽 | 芯片1脚 | 锁紧座放置位置     | 图中位置 |

|--------|-------|------|-------------|------|

| SOP16  | 不连接   | 左上角  | 锁紧座的下面8行    | 红框位置 |

| SOP8-1 | 连接1和2 | 左上角  | 锁紧座的 9~12 行 | 黄框位置 |

| SOP8-2 | 连接2和3 | 左上角  | 锁紧座的 9~12 行 | 黄框位置 |

2.3.1.2.2、配置卡-02: 烧录 1602、1605、1606、1607 芯片。支持封装 1602SOP8、1605SOP8、1606SOP8、1606SOP16、1606MSOP10、1607SOP8。

图 11. 配置卡-02 正面

图 12. 配置卡-02 背面

| 芯片封装       | 背面跳线帽 | 芯片1脚 | 锁紧座放置位置      | 图中位置 |

|------------|-------|------|--------------|------|

| 1602SOP8   | 连接2和3 | 左上角  | 锁紧座的 10~13 行 | 黄框位置 |

| 1605SOP8   | 连接2和3 | 左上角  | 锁紧座的 10~13 行 | 黄框位置 |

| 1606SOP8   | 不连接   | 左上角  | 锁紧座的 5~8 行   | 绿框位置 |

| 1606SOP16  | 不连接   | 左上角  | 锁紧座的下面8行     | 红框位置 |

| 1606MSOP10 | 连接1和2 | 左上角  | 锁紧座的 9~13 行  | 蓝框位置 |

| 1607SOP8   | 不连接   | 左上角  | 锁紧座的 5~8 行   | 绿框位置 |

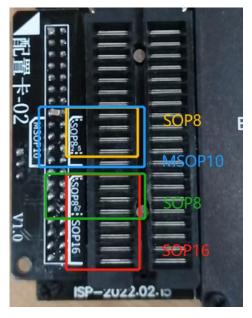

2.3.1.2.3: 配置卡-03: 烧录 18F02、18F020、18F022 芯片。支持封装 SOP16、QFN20、TSSOP20。

第 11 页 共 33 页

图 13. 配置卡-03 正面

图 14. 配置卡-03 背面

| 封装      | 背面跳线帽 | 芯片1脚 | 锁紧座放置位置     | 图中位置 |

|---------|-------|------|-------------|------|

| SOP16   | 连接2和3 | 左上角  | 锁紧座的靠下8行    | 红框位置 |

| TSSOP20 | 连接1和2 | 左上角  | 锁紧座的 5~14 行 | 黄框位置 |

| QFN20   | 连接1和2 | 左上角  | 锁紧座的靠下 10 行 | 蓝框位置 |

2.3.1.2.4: 配置卡-04: 烧录 16F01 芯片。支持封装 SOP8、SOP14。

图 15. 配置卡-04 正面

| 封装       | 芯片1脚         | 锁紧座放置位置      | 图中位置 |

|----------|--------------|--------------|------|

| SOP14    | 左上角 锁紧座的靠下7行 |              | 红框位置 |

| SOP8 左上角 |              | 锁紧座的 11-14 行 | 蓝框位置 |

| SOT23-6  | 左上角          | 锁紧座的 8-10 行  | 黄框位置 |

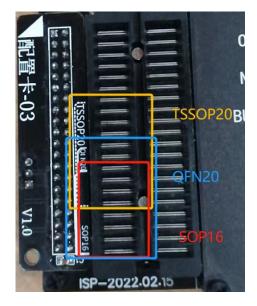

2.3.1.2.5: 配置卡-05-1: 烧录 18F06 芯片。支持封装 SSOP28、LQFP32

图 16. 配置卡-05-1

| 封装     | 芯片1脚 | 锁紧座放置位置     | 图中位置 |

|--------|------|-------------|------|

| SSOP28 | 右下角  | 锁紧座的靠下 14 行 | 红框位置 |

| LQFP32 | 右下角  | 锁紧座的靠下 17 行 | 黄框位置 |

2.3.1.2.6: 配置卡-06: 烧录 18F08 芯片。支持封装 SOP16、MSOP10、QFN16

图 17. 配置卡-06 正面

图 18. 配置卡-06 反面

| 封装     | 芯片1脚 | 锁紧座放置位置      | 图中位置 |

|--------|------|--------------|------|

| SOP8   | 左上角  | 锁紧座的靠下 11-14 | 白框位置 |

|        |      | 行            |      |

| SOP16  | 左上角  | 锁紧座的 3-10 行  | 红框位置 |

| MSOP10 | 左上角  | 锁紧座的 6-10 行  | 黄框位置 |

| QFN16  | 左上角  | 锁紧座的 7-14 行  | 蓝框位置 |

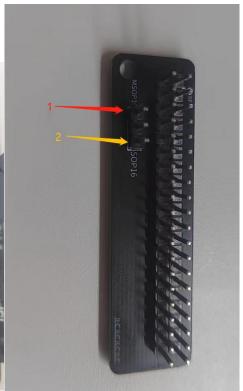

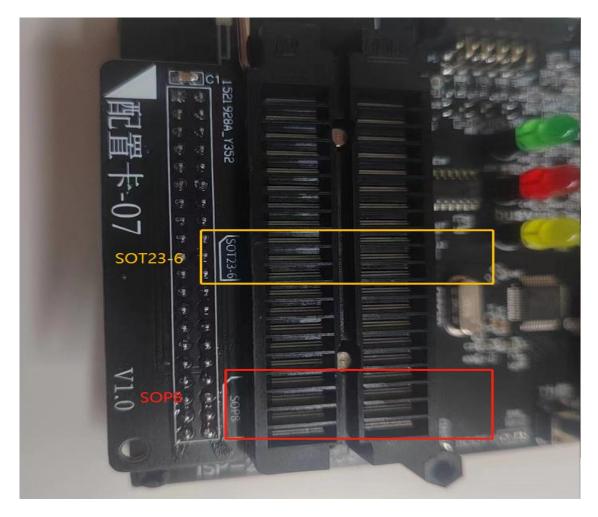

2.3.1.2.7: 配置卡-07: 烧录 16F02 芯片。支持封装 SOP8、SOT23-6

图 19. 配置卡-07

| 封装      | 芯片1脚 | 锁紧座放置位置      | 图中位置 |

|---------|------|--------------|------|

| SOP8    | 左上角  | 锁紧座的靠下4行     | 红框位置 |

| SOT23-6 | 左上角  | 锁紧座的靠下 10-12 | 黄框位置 |

|         |      | 行            |      |

### 2.3.2 在线烧录

以下用 1606 SOP16 芯片举例说明手工在线烧录的过程。除 18F02 外其他型号芯片烧录空片和烧录经过 FT 的芯片的操作方法是一致的,不同的是 ISP 上提示信息,空片会经过校准, FT 过的芯片只需要进行烧录,具体信息解析见 2.3.2.7。18F02 烧录空片时需要选择 CKOE 为 PB4(ISP 下通用设置中),烧录 FT 芯片时不用接 CKOE。信息解析同 2.3.2.7。

2.3.2.1: 在线烧录 1606 SOP16 芯片时,还将用到 SOP16 座子。将芯片放到 SOP16 座子

上(请注意 PIN1 方向朝左上角),座子底端对齐。

图 20. SOP16 烧录座

- 2.3.2.2: 插上对应的配置卡。按照配置卡上对应的放置范围放置(见 2.3 节)。

- 2.3.2.3: 将锁紧座杆向上拨动,打开锁紧座,然后将装好芯片的烧录座插到锁紧座中,把锁紧座杆向下拨动,锁住烧录座,连接好的实物见下图(注意:不同封装的烧录座插到锁紧座上时请按照红色箭头限定的范围)。

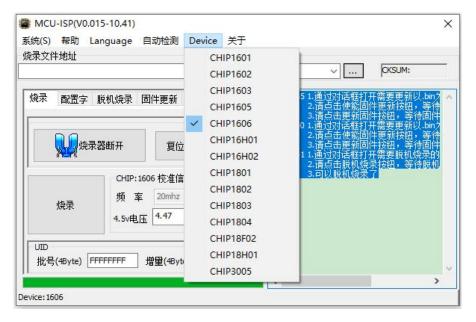

2.3.2.4: 按照图 21,选择芯片型号 "CHIP1606",成功选择后,左下角会显示"Device: 1606"字样。

图 21. 选择芯片型号

2.3.2.5: 按照图 22, 在烧录选项卡界面, 先选择要烧录的程序文件(HEX 文件), 然后点击"烧录",即可进行烧录操作。使用相同烧录器,再次烧录相同的程序文件给其它 1606 芯片时,只需要点击"烧录"按钮,无需再进行前两步的操作。

图 22. 在线烧录步骤

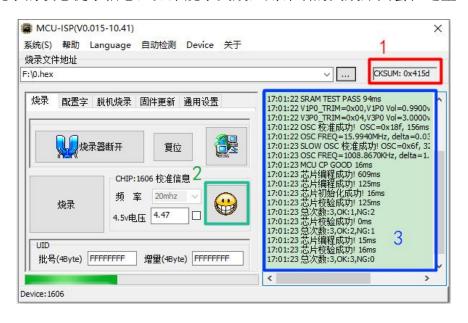

2.3.2.6: 烧录前结果: 正常情况下, 烧录结束后, 界面如图 23 所示。红框 1 显示的是当

前 HEX 文件的校验码;绿框 2 显示本次烧录的结果,OK 为图标,NG 为图标,NG 为同时烧录器上的烧录指示灯也会提示,OK 亮绿灯,NG 亮红灯,正在烧录亮黄灯。蓝框 3 显

示的是本次烧录的状态提示信息,如果烧录失败,则详细的失败原因会在这里显示。

图 23. 在线烧录结果

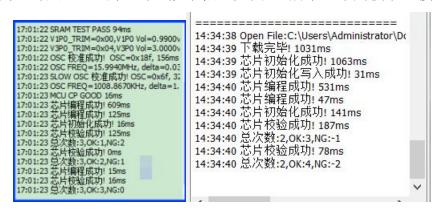

2.3.2.7: 烧录提示信息解析: 若烧录的芯片是空片, 烧录信息如图 24 所示, 先校准再进行烧录; 若烧录的芯片是 FT 过的芯片, 烧录信息如图 25 所示, 不用校准直接进行烧录。

图 24. 空片烧录信息 图 25. 空片烧录信息

2.3.2.8: 若烧录成功后,未更换芯片,再次点击烧录按钮,烧录器会自动判断当前芯片已经烧录过一次了,不会再次进行烧录动作,只执行校验动作。信息栏的文字如图 26 所示。

图 26. 二次烧录时的提示信息

2.3.2.9: 烧录器 OLED 屏幕在烧录结束时,也会有相应信息显示,具体如图 27 所示。

图 27. OLED 屏幕显示烧录结果

黄色 1 指示的文字表示读取到当前芯片内已烧录程序的校验码;

蓝色 2 指示的文字表示上位机传到烧录器的程序文件,或烧录器内部存储的脱机烧录文件数据,经过计算后,得出的校验码;

- 紫色 3 指示的文字表示本次烧录的结果, OK 还是 NG:

- 绿色 4 指示的文字表示累计烧录 OK 的次数;

- 红色 5 指示的文字表示累计烧录 NG 的次数;

- 橙色 6 指示的文字表示给已经烧录程序的芯片再次烧录相同程序时的累计次数,即二次烧录时,执行校验动作的累计次数。

- 2.3.2.10: 其他型号芯片烧录与 1606 过程基本一致。硬件上的区别是需要使用对应型号的配置卡,软件上的区别就是烧录器需要使用对应的固件以及烧录 hex。不同封装的芯片烧录时需要使用不同的烧录座,比如 18F02 TSSOP20 封装烧录时需要用到 TSSOP20 烧录座。

图 28. 放入烧录座中的 TSSOP20 芯片

#### 2.3.3 脱机烧录

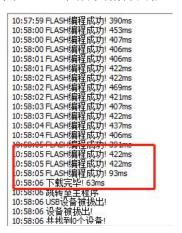

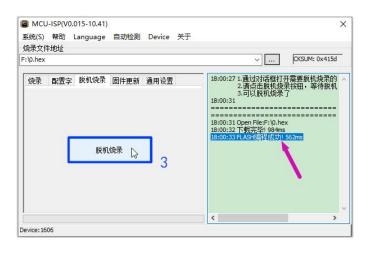

2.3.3.1: 下载 hex: 先将烧录器连接 12V 电源, 再与电脑连接。与在线烧录类似, 在"Device" 菜单中, 先选择要烧录的芯片型号, 接着选择要烧录的程序文件, 然后在"脱机烧录"选项卡里(图 29), 点击"脱机烧录"按钮(图 30), 等待信息栏出现" FLASH 编程成功"字样后, 则说明脱机烧录文件成功写入到烧录器中。

图 29. 脱机烧录步骤

图 30. 脱机烧录步骤

第 20 页 共 33 页

2.3.3.2: 手工脱机烧录: 先将芯片连接到烧录器上,具体的连接方法与在线烧录时保持一致,然后只需要按下图 31 中红框所示的按键,即可进行烧录。可以通过 OLED 屏幕看到烧录的结果。详细信息见图 27 所示。

图 31. 手工脱机烧录按键

#### 2.3.3.3: 机台脱机烧录:

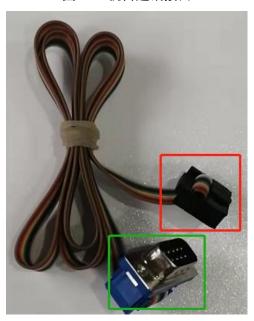

1、需要用到烧录器上的机台通讯接口,如图 32 所示。红框位置是烧录器的机台连接位置,使用图 33 所示的连接线的红框一端连接烧录器,绿框一端连接机台。烧录的结果同样可以通过 OLED 屏幕和烧录指示灯看到,OLED 屏幕的详细信息见图 27 所示。

图 32. 机台通讯接口

图 33. 机台、烧录器连接线

2、机台的配置信息,以金创图为例,可以参考如下配置。

第 21 页 共 33 页

图 34. 烧录器 ID 设置参考

图 35. 烧录器电平及持续时间设置参考

## 2.4 接线烧录

芯片按照如下方式接线,确定连接无误后,按照 2.3.2 在线烧录和 2.3.3 脱机烧录的方式进行烧录。

#### 2.4.1 1605、1606、1607 接线烧录

1605、1606、1607的烧录引脚见图 36。这三款烧录空片和烧录 FT 过的芯片的接法是一致的。总共有两种接法,可以根据自己的条件选择具体方法。

| 序号 | 烧录引脚 | 烧录信号    | 在板说明                                                            |

|----|------|---------|-----------------------------------------------------------------|

| 1  | VCC  | VCC     | VCC Pin和Vss Pin,在烧录时,烧录器会先供4.5V电压用于建立连接与参数校准,再供7.6V电压,用于烧录HEX程  |

| 2  | VSS  | GND     | 序。因此,要确保电路中,与VCC Pin相连的其它器件,要能承受住7.6V电压;                        |

| 3  | PB0  | CS      | PB0 Pin是CS(片选),该引脚走线上不建议连接0.1uf以上的电容。不允许连接强上拉/下拉电阻。             |

| 4  | PB2  | CKOE    | PB2 Pin是PWM输出,频率约1KHz左右,该引脚走线不允许出现电容,不允许出现强上拉/下拉电阻。             |

| 5  | PB5  | DAT_IN  | PB5 Pin是Data IN(对于1605而言),该引脚不建议连接<br>0.1uf以上的电容。不允许连接强上拉/下拉电阻。 |

| 6  | PB3  | DAT_OUT | PB3 Pin是Data OUT(对于1605而言),该引脚不建议连接0.1uf以上的电容。不允许连接强上拉/下拉电阻。    |

| 7  | PB4  | CLK     | PB4 Pin 是 CLK,约600K,该引脚走线不允许出现电容,不允许出现强上拉/下拉电阻。                 |

图 36.1605、1606、1607 烧录引脚

2.4.1.1: 锁紧座旁边接线;按照下图 37 所示,接到芯片的对应烧录引脚进行烧录。

图 37. 锁紧座旁接线烧录

2.4.1.2: ISP 接口接线;找到如下图 38 烧录器侧边的 ISP 接口,根据下图 39 的接口定义接到芯片的烧录引脚。两者的对应关系为:

| ISP 接口  | 芯片引脚 | ISP 接口  | 芯片引脚 |

|---------|------|---------|------|

| V1:7.5V | VCC  | GND     | GND  |

| S1:CLK  | PB4  | S2:DAT  | PB5  |

| S3:CKOE | PB2  | S4:RST- | PB3  |

| S5:CS   | PB0  |         |      |

图 39. ISP 接口定义

#### 2.4.2 16H02 接线烧录

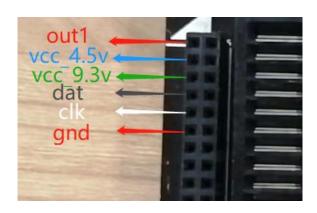

16H02的烧录引脚见图 40。这款芯片烧录空片和烧录 FT 过的芯片的接法是一致的。

| 序号 | 烧录引脚              | 烧录信号    | 在板烧录说明                                                                                                   |

|----|-------------------|---------|----------------------------------------------------------------------------------------------------------|

| 1  | VCC               | VCC_4.5 |                                                                                                          |

| 2  | VSS2(SOP16)/GND   | GND     | 16H02 在烧录时,烧录器会提供两种电源,一种是 4.5V 电压用于建立连接与参数校准,一种供 9.3V 电压,用于烧录 HEX 程序。因此,要确保电路中,与这两种电源相连的其它器件,要能承受住相应的电压; |

| 3  | VIN2/VIN1(SOP8-2) | VCC_9.3 |                                                                                                          |

| 4  | PB4               | DAT     | PB4 Pin 是 Data,该引脚不建议连接 0.1uf 以上的电容。不允许连接强上拉/下拉电阻。                                                       |

| 5  | PB5               | CLK     | PB5 Pin 是 CLK,该引脚走线不允许出现电容,不允许出现强上拉/下拉电阻。                                                                |

| 6  | OUT1              | CKOE    | OUT1 Pin 是 PWM 输出,频率约 1KHz 左右,该引脚走线不允许出现电容,不允许出现强上拉/下拉电阻。                                                |

注: VCC\_9.3 注意事项 封装: SOP8-2;接 VIN1; 其余封装接 VIN2; VSS2 注意事项 封装: SOP16; 接 VSS2; 其余封装接 GND;

图 40. 16H02 烧录引脚

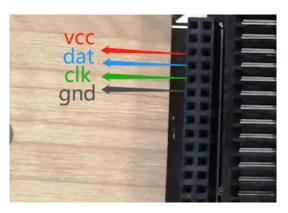

2.4.2.1: 锁紧座旁边接线;按照下图 41 所示,接到芯片的对应烧录引脚进行烧录。

图 41. 锁紧座旁接线烧录

2.4.2.2: ISP 接口接线; 找到如上图 38 烧录器侧边的 ISP 接口,根据上图 39 的接口定义接到芯片的烧录引脚。两者的对应关系为:

| ISP 接口  | 芯片引脚    | ISP 接口   | 芯片引脚    |

|---------|---------|----------|---------|

| V1:7.5V | VCC_9.3 | GND      | GND     |

| S1:CLK  | PB5     | S2:DAT   | PB4     |

| S3:CKOE | OUT1    | V2:4.5V- | VCC_4.5 |

## 2.4.3 18F02、18F020、18F022, 18F128 接线烧录

18F02、18F020、18F022 的烧录引脚见图 42。这三款芯片烧录空片和烧录 FT 过的芯片的接法是不一致的。

| 序号 | 烧录引脚 | 烧录信号 | 在板说明                                                                              |

|----|------|------|-----------------------------------------------------------------------------------|

| 1  | VCC  | VCC  | VCC Pin 和 Vss Pin 在烧录时,电压会变化,因此必须由烧录器VCC 直接连接到芯片VCC 。在烧录时,烧录器会断电                  |

| 2  | VSS  | GND  | 再上电做检查,因此并联的电容建议不要超过470uF电容,<br>电容越大,烧录时间越长。                                      |

| 3  | PA2  | DAT  | CLK,DAT,为通信线,不允许0.1uF以上的电容,不允许强                                                   |

| 4  | PA3  | CLK  | 上下拉电阻。                                                                            |

| 5  | PB4  | CKOE | CKOE可以是任意脚位(不包括VCC VSS PA2 PA3)。校准<br>芯片时会产生1KHZ方波,电容会影响波形,因此禁止电容<br>并联,也禁止上下拉电阻。 |

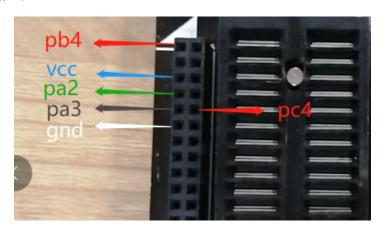

图 42. 18F02 烧录引脚

#### 2.4.3.1: 锁紧座旁边接线;

1、烧录空片时,需要先进行校准,再烧录。接线方法按照下图 43 所示,接到芯片的对应烧录引脚进行烧录。

图 43. 空片锁紧座旁接线烧录

2、烧录 FT 芯片时,直接进行烧录。接线方法按照下图 44 所示,接到芯片的对应烧录引脚进行烧录。

图 44. FT 芯片锁紧座旁接线烧录

2.4.3.2: ISP 接口接线, 烧录空片时, 不能从 ISP 接口这边接线。FT 芯片找到如上图 38 烧录器侧边的 ISP 接口, 根据上图 39 的接口定义接到芯片的烧录引脚。

| ISP 接口   | 芯片引脚 | ISP: | 接口    芯片引脚 |

|----------|------|------|------------|

| V2:4.5V- | VCC  | GN   | ND GND     |

| S1:CLK   | PA3  | S2:I | PA2        |

## 2.4.4 16F01 接线烧录

16F01 的烧录引脚见图 45。这款烧录空片和烧录 FT 过的芯片的接法是不一致的。

| 序号 | 烧录引脚 | 烧录信号 | 在版说明                                                                      |

|----|------|------|---------------------------------------------------------------------------|

| 1  | VCC  | VCC  | VCC pin和Vss pin在烧录时,电压会变化,因此必须由烧录器Vcc直接连接                                 |

| 2  | VSS  | GND  | 到芯片vcc,在烧录时,烧录器会断电再上电做检查,因此并联的电容不建议<br>超过470uF电容,电容越大,烧录时间越长              |

| 3  | PA1  | CLK  |                                                                           |

| 4  | PA2  | DAT  | -CLK DAT.为通信线,不允许0.1uF以上的电容,不允许强上下拉电阻                                     |

| 5  | PB0  | BGR  |                                                                           |

| 6  | PB5  | CKOE | CKOE可以是任意脚位(不包括vcc vss PA1 PA2).校准芯片时会产生1KHZ方波,电容会影响波形,因此禁止电容并联,也禁止上下拉电阻。 |

注: 封装: SOT23-6 时 CKOE 接 PA0

图 45 16F01 接线引脚

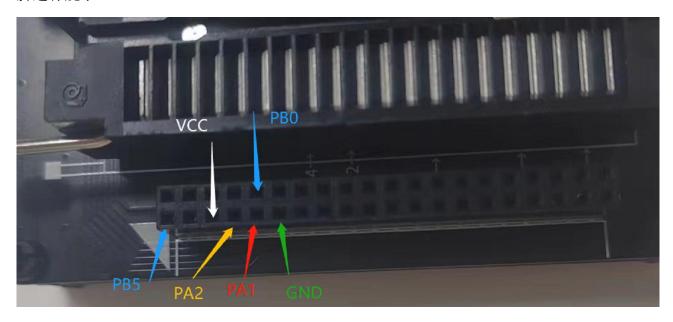

#### 2.4.4.1 锁紧座旁边接线;

烧录空片时,需要先进行校准,再烧录。接线方法按照下图 46 所示,接到芯片的对应烧录引脚进行烧录。

图 46 16F01 接线引脚

2、烧录 FT 芯片时,直接进行烧录。接线方法按照下图 47 所示,接到芯片的对应烧录引脚进行烧录

图 47 16F01 接线引脚

2.4.4.2 ISP 接口接线;找到如上图 38 烧录器侧边的 ISP 接口,根据上图 39 的接口定义接到芯片的烧录引脚。两者的对应关系为:

| ISP 接口  | 芯片引脚 | ISP 接口 | 芯片引脚 |

|---------|------|--------|------|

| V2:4.5V | VCC  | GND    | GND  |

| S1:CLK  | PA1  | S2:DAT | PA2  |

| S3:CKOE | PB5  |        |      |

## 2.4.5 18F06 接线烧录

18F06 的烧录引脚见图 48。这款烧录空片和烧录 FT 过的芯片的接法是不一致的。

| 序号 | 烧录引脚 | 烧录信号 | 在版说明                                                                       |

|----|------|------|----------------------------------------------------------------------------|

| 1  | vcc  | VCC  | VCC pin和VSS pin在烧录时,电压会变化,因此必须由烧录器VCC直接连接到芯片                               |

| 2  | VSS  | GND  | VCC, 在烧录时, 烧录器会断电再上电做检查, 因此并联的电容不建议超过470uF电容, 电容越大, 烧录时间越长                 |

| 3  | PA0  | DAT  | PAO Pin是data,该引脚不建议连接0.1uf以上的电容,不允许连接强上拉/下拉电阻                              |

| 4  | PA1  | BGR  |                                                                            |

| 5  | PA2  | CLK  | PA2 Pin是CLK,该引脚走线不允许出现电容,不允许出现强上拉/下拉电阻                                     |

| 6  | РВО  | CKOE | CKOE可以是任意脚位 (不包括vcc vss PA1 PA2).校准芯片时会产生1KHZ方波,电容会影响波形,因此禁止电容并联,也禁止上下拉电阻。 |

#### 图 48 18F06 接线引脚

#### 2.4.5.1 锁紧座旁边接线;

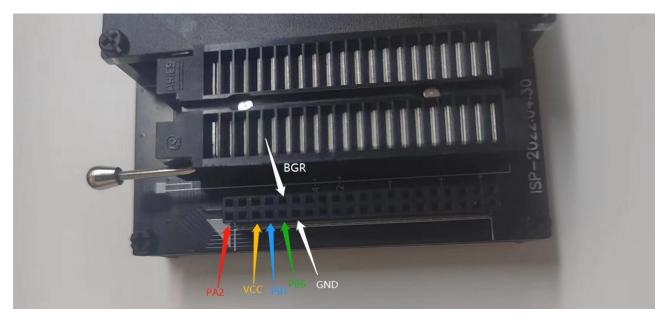

烧录空片时,需要先进行校准,再烧录。接线方法按照下图 49 所示,接到芯片的对应烧录引脚进行烧录。

图 49 18F06 接线引脚

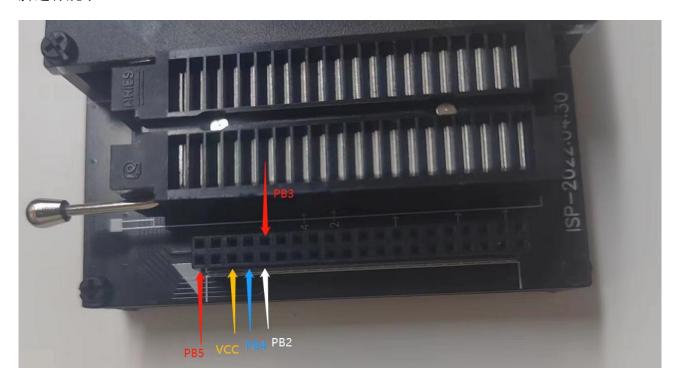

2.烧录 FT 芯片时,直接进行烧录。接线方法按照下图 50 所示,接到芯片的对应烧录引脚进行烧录

第 29 页 共 33 页

#### 图 50 18F06 接线引脚

2.4.5.2 ISP 接口接线;找到如上图 38 烧录器侧边的 ISP 接口,根据上图 39 的接口定义接到芯片的烧录引脚。两者的对应关系为:

| ISP 接口  | 芯片引脚 | ISP 接口 | 芯片引脚 |

|---------|------|--------|------|

| V2:4.5V | VCC  | GND    | GND  |

| S1:CLK  | PA2  | S2:DAT | PA0  |

| S3:CKOE | PB0  |        |      |

### 2.4.6 18F08 接线烧录

18F08 的烧录引脚见图 51。这款烧录空片和烧录 FT 过的芯片的接法是不一致的。

| 序号 | 烧录引脚 | 烧录信号 | 在版说明                                                                          |

|----|------|------|-------------------------------------------------------------------------------|

| 1  | VCC  | VCC  | VCC pin和VSS pin在烧录时,电压会变化,因此必须由烧录器VCC直接连接到芯片                                  |

| 2  | VSS  | GND  | VCC,在烧录时,烧录器会断电再上电做检查,因此并联的电容不建议超过470uF电容,电容越大,烧录时间越长                         |

| 3  | PB7  | DAT  | PAO Pin是data,该引脚不建议连接0.1uf以上的电容,不允许连接强上拉/下拉电阻                                 |

| 4  | PB3  | BGR  |                                                                               |

| 5  | PB6  | CLK  | PA2 Pin是CLK,该引脚走线不允许出现电容,不允许出现强上拉/下拉电阻                                        |

| 6  | PA2  | CKOE | CKOE可以是任意脚位 (不包括vcc vss PA1 PA2).校准芯片时会产生1KHZ方波, 电容会影响波形, 因此禁止电容并联, 也禁止上下拉电阻。 |

图 51 18F08 接线引脚

#### 2.4.6.1 锁紧座旁边接线;

烧录空片时,需要先进行校准,再烧录。接线方法按照下图 52 所示,接到芯片的对应烧录引脚进行烧录。

图 52 18F08 接线引脚

2.烧录 FT 芯片时,直接进行烧录。接线方法按照下图 53 所示,接到芯片的对应烧录引脚进 行烧录

图 53 18F08 接线引脚

2.4.6.2 ISP 接口接线;找到如上图 38 烧录器侧边的 ISP 接口,根据上图 39 的接口定义接到芯片的烧录引脚。两者的对应关系为:

| ISP 接口  | 芯片引脚 | ISP 接口 | 芯片引脚 |

|---------|------|--------|------|

| V2:4.5V | VCC  | GND    | GND  |

| S1:CLK  | PB6 | S2:DAT | PB7 |

|---------|-----|--------|-----|

| S3:CKOE | PA2 |        |     |

### 2.4.7 16F02 接线烧录

16F02 的烧录引脚见图 54。这款烧录空片和烧录 FT 过的芯片的接法是不一致的。

| 序号 | 烧录引脚 | 烧录信号 | 在版说明                                                                      |  |

|----|------|------|---------------------------------------------------------------------------|--|

| 1  | VCC  | vcc  | VCC pin和VSS pin在烧录时,电压会变化,因此必须由烧录器VCC直接连接到芯片                              |  |

| 2  | VSS  | GND  | YCC, 在烧录时, 烧录器会断电再上电做检查, 因此并联的电容不建议超过470uF电容, 电容越大, 烧录时间越长                |  |

| 3  | PB4  | DAT  | CLV DAT 为语信线。不公为0.1,EDJ E的中央。不公为程上下拉中阳                                    |  |

| 4  | PB2  | CLK  | CLK DAT.为通信线,不允许0.1uF以上的电容,不允许强上下拉电阻                                      |  |

| 5  | PB3  | BGR  |                                                                           |  |

| 6  | PB5  | СКОЕ | CKOE可以是任意脚位(不包括vcc vss PA1 PA2).校准芯片时会产生1KHZ方波,电容会影响波形,因此禁止电容并联,也禁止上下拉电阻。 |  |

图 54 16F02 接线引脚

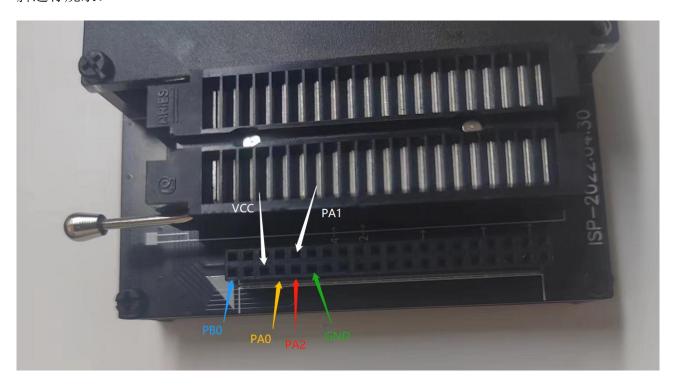

#### 2.4.7.1 锁紧座旁边接线;

烧录空片时,需要先进行校准,再烧录。接线方法按照下图 55 所示,接到芯片的对应烧录引脚进行烧录。

图 55 16F02 接线引脚

2.烧录 FT 芯片时,直接进行烧录。接线方法按照下图 56 所示,接到芯片的对应烧录引脚进 行烧录

图 56 16F02 接线引脚

2.4.7.2 ISP 接口接线;找到如上图 38 烧录器侧边的 ISP 接口,根据上图 39 的接口定义接到芯片的烧录引脚。两者的对应关系为:

| ISP 接口  | 芯片引脚 | ISP 接口 | 芯片引脚 |

|---------|------|--------|------|

| V2:4.5V | VCC  | GND    | GND  |

| S1:CLK  | PB2  | S2:DAT | PB4  |

| S3:CKOE | PB5  |        |      |

注意事项: 16F02 载板烧录时须在 VCC GND 近端加入最小 1uf 的电容(如不加会导致初始化失败)。CLK,DAT 为通讯线不建议强上下拉电阻。